### EE 222 Lecture 15 Feb. 26, 2019 LOW POWER DESIGN of Logic Circuits:

- · Combinational circuits

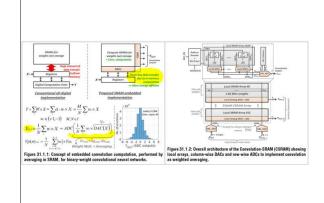

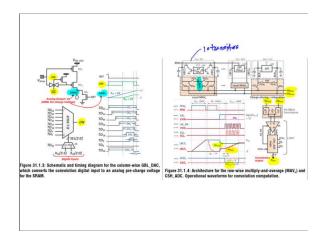

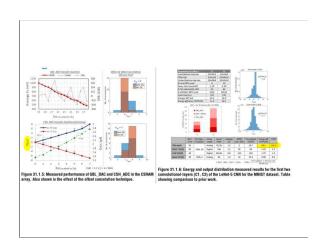

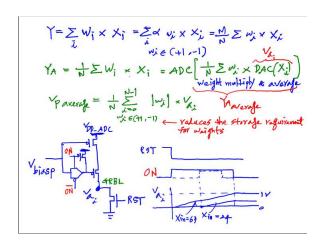

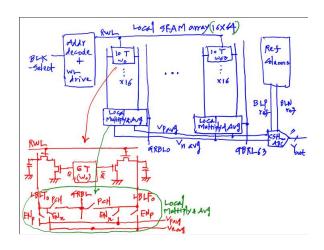

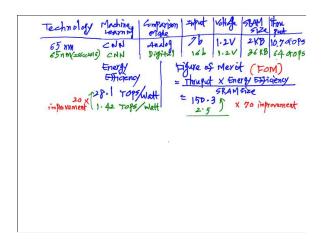

- Mixed signal (digital and analog) circuits for processing in memory (PIM)

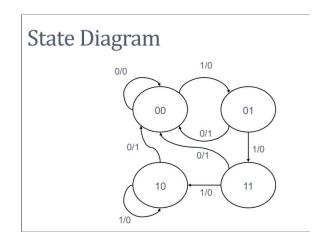

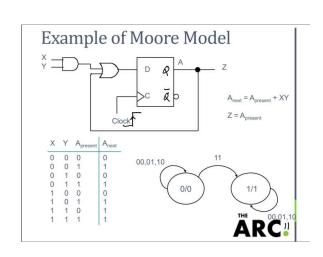

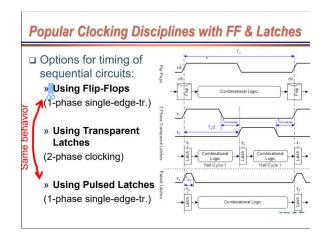

sequential circuits

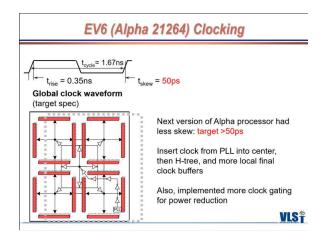

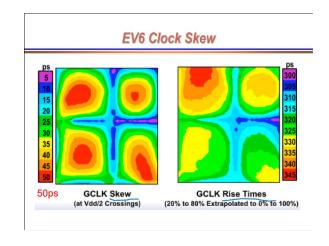

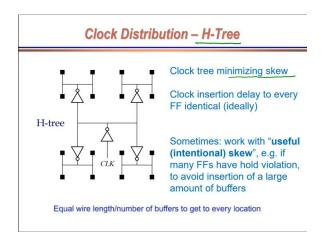

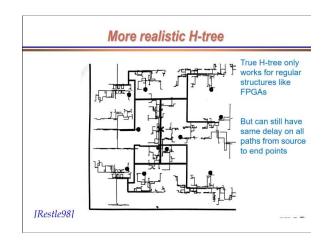

- · clock distribution

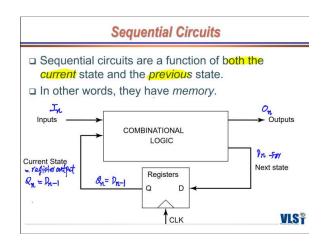

### **Combinational Vs. Sequential Circuits**

### Combinational (or Combinatorial) Networks/Circuits

- · Circuit without storage

- · Outputs depend only on its current inputs

- · Examples: NAND gate, look-up table (LUT)

Vs.

### Sequential Networks/Circuits

- Circuit with storage elements

- Outputs depend on present inputs and also on history of inputs

- · Examples: RAM, finite state machine (FSM)

- · Normally, combinational cells AND storage elements

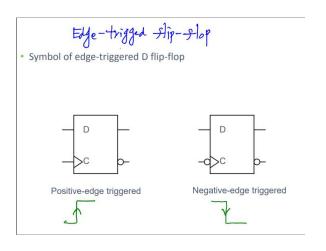

### Flip-Flop Timing • Set-up time: t<sub>s</sub> • Input needs to be stable before trigger • Hold time: t<sub>h</sub> • Input needs to be stable after trigger • Propagation delay: t<sub>p</sub> • Some delay from trigger to output change • Example: Negative edge triggered flip-flip

### References II J. Yuan and C. Svensson, "High-speed CMOS circuit technique," IEEE J. Solid-State Circuits, vol. 24, pp. 62–70, Feb. 1989. IZ Y. Suzuki, K. Odagawa, and T. Abe, "Clocked CMOS calculator circuitry," IEEE J. Solid-State Circuits, vol. 8, pp. 462–469, Dec. 1973. IR. H. Krambeck, C. M. Lee, and H. S. Law, "High-speed compact circuits with CMOS," IEEE J. Solid-State Circuits, vol. 17, pp. 614–619, June 1982. IM. Shoji, CMOS Digital Circuit Technology. Englewood Cliffs, NJ: Prentice Hall, 1988. IS N. P. Goncalves and H. J. de Man, "NORA: A racefree dynamic CMOS technique for pipelined logic structures," IEEE J. Solid-State Circuits, vol. 18, pp. 261–268, June 1983.

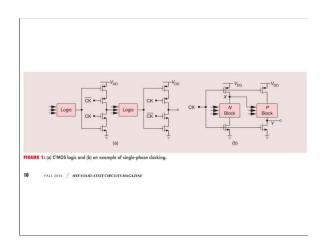

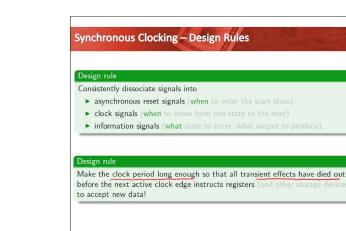

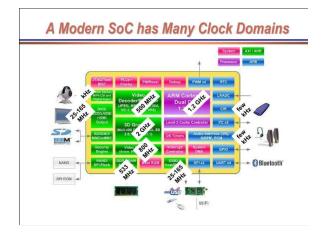

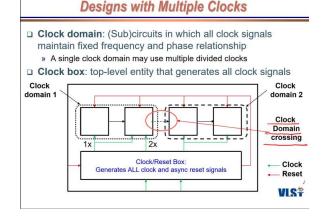

## Definitions: A (sub)circuit is said to operate synchronously iff all state transitions are restricted to occur periodically at precise moments of time that are determined by a special signal referred to as the clock. A clock domain is a (sub)circuit where all clock signals maintain fixed frequency and phase relationships because they are derived from a common source.

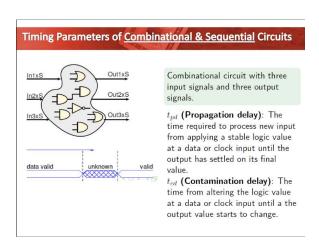

### Timing Quantities - Comb. and Seq. Circuits

### Combinational and sequential circuits

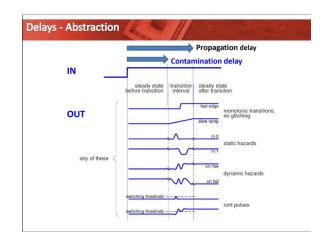

Propagation delay tpd

- New stable input (data or clock) output settled on final value

- Example NAND: A-to-Z, and B-to-Z

- Example latch: D-to-Q, and/or CLK-to-Q

Contamination delay (or retain delay) tcd

- Altering input (data or clock) first change of value at output

- By definition: 0≤tcd ≤tpd

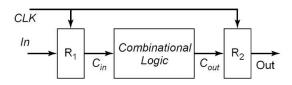

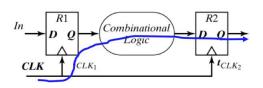

### Synchronous Timing

Synchronous timing:

All registers synchronized with same CLK

### Timing Constraints (Setup & Hold)

- ☐ There are two main problems that can possibly arise in

- synchronous logic:

» Max Delay: The data doesn't have enough time to pass from one register to the next before the next clock edge.

- » Min Delay: The data path is so short that it causes a hold violation in capturing register.

- Max delay violations are a result of a slow (long) data paths, including the register's  $t_{su}$ , therefore they are often called "Setup violations".

- ☐ Min delay violations are a result of a fast (short) data path, causing the data to change before the  $t_{\it hold}$  of the reg has passed, therefore they are often called the "Hold violations".

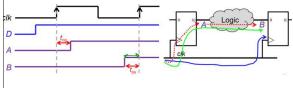

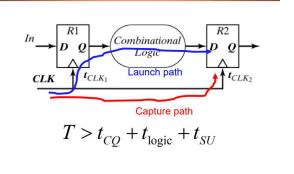

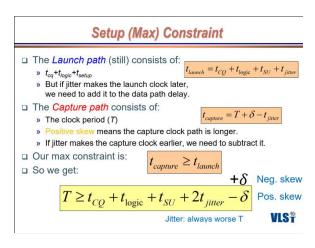

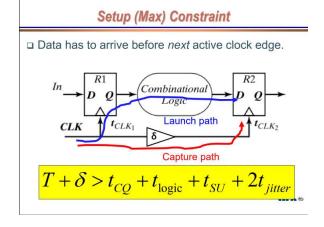

### Setup (Max) Constraint

- □ Let's see what makes up our clock cycle:

- » After the clock rises, it takes  $t_{cq}$  for the data to propagate to point A.

- » Then the data goes through the delay of the logic to get to point B.

- » The data has to arrive at point  $B t_{su}$  before the next clock edge.

- □ In general, our timing path is a race:

- » Between the Data Arrival, starting with the launching clock edge.

- » And the Data Capture, one clock period later.

### Setup (Max) Constraint

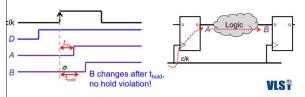

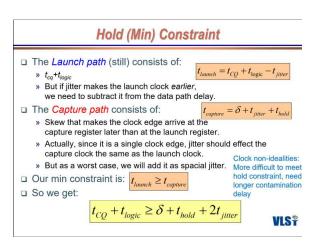

### Hold (Min) Constraint

- $\Box$  Hold problems occur due to the logic changing before  $t_{hold}$  has passed.

- □ This is not a function of cycle time it is relative to a single clock edge!

- □ Example of meeting the hold constraint:

- » The clock rises and the data at A changes after  $t_{ca}$

- » The data at B changes tpd(logic) later.

- Since the data at B had to stay stable for t<sub>hold</sub> after the clock (for the second register), the change at B has to be at least t<sub>hold</sub> after the clock edge.

### Hold (Min) Constraint

$$t_{CQ} + t_{\rm logic} > t_{hold}$$

### Summary

- □ For Setup constraints, the clock period has to be longer than the data path delay:  $T > t_{CQ} + t_{\text{logic}} + t_{SU}$

- » This sets our maximum frequency.

- » If we have setup failures, we can always just slow down the clock.

- □ For Hold constrains, the data path delay has to be longer than the hold time:

- » This is independent of clock period.  $|t_{CQ} + t_{

m logic}| > t_{hold}$

$$t_{CQ} + t_{\text{logic}} > t_{hold}$$

» If there is a hold failure, your chip will never work!

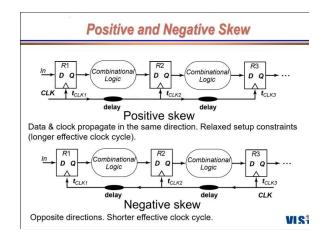

### Fundamental Timing Conditions - Reminder $t_{clk} \geqslant t_{pd_{ff}} + t_{pd_c} + t_{su_{ff}} \left( -t_{sk} \right)$ 5 Kew Hold Condition $t_{ho_{ff}} \leqslant t_{cd_{ff}} + t_{cd_{c}} \left( -t_{sk} \right)$ Positive clock skew $t_{sk}$ relaxes The formulas to the right apply to the data input of register U2. the setup condition, while having detrimental effects on the hold condition.

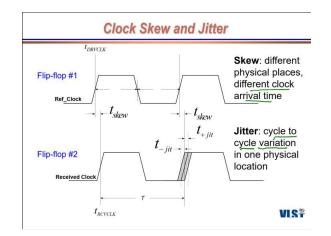

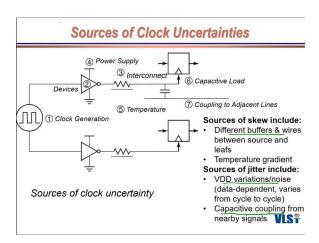

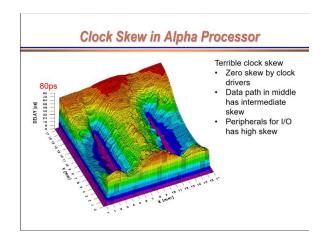

### □ Clock skew

» Spatial variation in temporally equivalent clock edges; deterministic (can control it) + random,  $t_{SK}$

### □ Clock jitter

- » Temporal variations in consecutive edges of the clock signal; purely random

- » Cycle-to-cycle (short-term)  $t_{JS}$

- » Long term t<sub>JI</sub>

Both skew and jitter affect the effective cycle time

### Variation of the pulse width

» Important for level-sensitive clocking (latches)

VLST

###

## Ref\_Clock Received Clock Digital System Clocking: Oklobdzija, Stojanovic, Markovic, Nedovictics Reversed Clock Received Cl

### Hold (Min) Constraint Data has to arrive after same clock edge has arrived at capturing register $In \longrightarrow D Q \qquad Combinational \qquad R^2 \qquad D Q \qquad Combinational \qquad CLK \qquad Capture path$ Capture path Capture path Capture path

### Dealing with Skew and Jitter

- □ Balance clock paths using regular distribution network, such

- □ Use local clock GRIDS (increased cap and power)

- Route data and clock in opposite directions to improve hold at the expense of setup.

- □ Shield clock wires (minimize capacitive coupling)

- Use dummy metal density fillers for regular wires

- □ Use decoupling capacitors (for stable VDD)

- □ Time borrowing (or cycle stealing): long path borrows time from subsequent short path, accomplished using latches

- □ "Useful skew" to avoid expensive buffering for hold fix

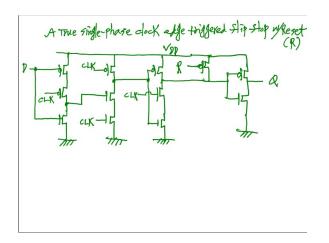

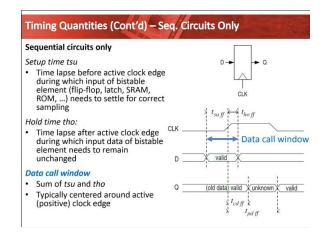

### Rising-edge-triggered D-type flip-flop The value at the input D becomes available at the output Q at the rising edge of the clock tsu (Set-up time): The lapse of time before the active clock edge during which an input is required to assume a fixed logic value of either 0 or 1 at the input of a clocked circuit. tho (Hold time): The lapse of time after the active clock edge during which data are required to remain logically unchanged at the input of a clocked circuit. Data call window: tsu + tho

# Clock Dividers Derive a slow clock from a fast clock by dividing it by an integer number (counter) Remember: all clocks (including divided clocks) need to be free of hzards and glitches Must assume that any logic can prodice glitches Generated (divided) clocks MUST come directly from a FF output

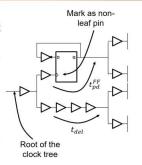

### Clock Dividers in the Clock Tree

- Clock and derived clock must be phase aligned at the clock roots

- Clock divider has a delay (FF propagation delay)

- » Need to consider clock divider during clock-tree generation

- Modern clock tree synthesis tools can trace through clock dividers

###

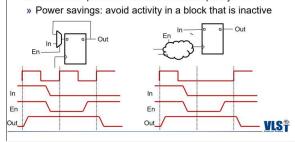

### **Clock Gating**

- □ Flip-Flops with ENABLE: prevent FlipFlop(s) from capturing new data

- » Functional: preserve content over multiple cycles

### **Clock Gating**

- □ Advantages:

- » Saves a multiplexer per FlipFlop with Enable (Area, Delay, and Power advantage)

- » Avoids activity on the clock net leading to the FlipFlop

- » Avoids activity on the FlipFlops clock pin reducing internal power consumption

- □ Disadvantages:

- » Need for additional logic to suppress the clock while FlipFlop is disabled (area and power penalty)

- » Need to ensure that the clock signal is free of glitches

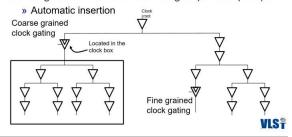

### ■ A safe strategy to realize clock gating

- » Latch on the Enable signal shields glitches during the sensitive period of the clock

- » Implemented with individual cells: some timing constraints need to be observed

- » Often realized as single dedicated library cell

**VLS**\*

### **Clock Gating**

- □ Cofase grained: disable entire blocks of the design

- » Inserted manually

- □ Fine grained: enable for small groups of FlipFlops

### Improving IO Timing

- □ Chip provides a clock output that is aligned with the clock at the leaves of the FlipFlops

- » Output of the clock output pad is declared as clock leaf

- » Delayed clock is used as a reference for rest of system

### **Improving IO Timing**

- □ Delay locked loop ( ) LL)

- » Generates a phase shifted clock such that the reference input is phase aligned with the input clock

- » Clock reference is taken from the leaves of the clock tree

- □ Internal clock at the leaves is aligned with clock input