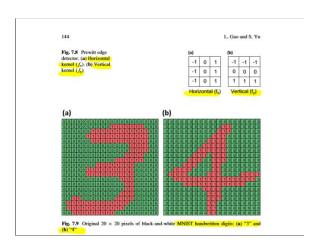

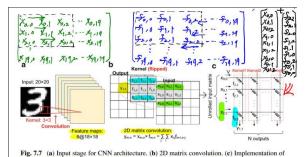

Fig. 7.7 (a) Input stage for CNN architecture. (b) 2D matrix convolution. (c) Implementation of convolution for multiple feature maps into a cross-point array architecture by reduction of 2D kernel matrix into 1D column vector

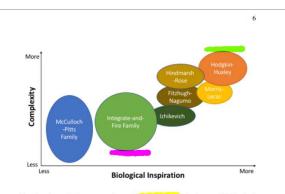

Fig. 5. A qualitative comparison of neuron models in terms of biological inspiration and complexity of the neuron model.

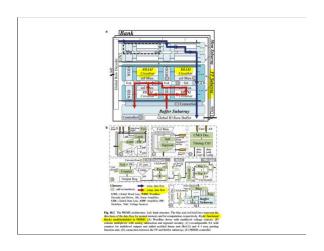

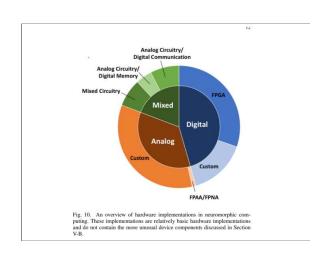

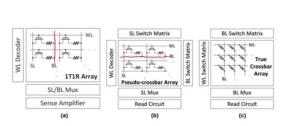

Fig. 9.1 Representative resistive NVM arrays with peripheral circuits are shown. (a) 1T1R array with row-by-row operation. (b) Pseudo-crossbar array implemented by rotating BL in 1T1R memory array. (c) True crossbar array without selector transistors for array-level parallelism

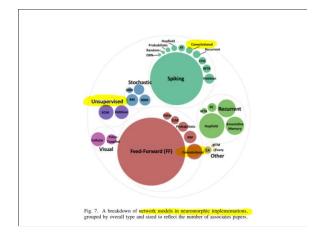

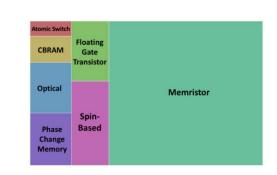

Fig. 11. Device-level components and their relative popularity in neuromorphic systems. The size of the boxes corresponds to the number of works referenced that have included those components.

Fig. 14. Examples from different image data sets (MNIST [2618], CIFAR10 [2619], and SVHN [2620]) to which neuromorphic systems have been applied for classification purposes.

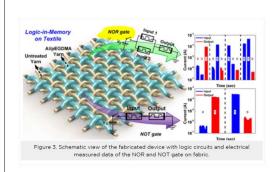

## Functional Circuitry on Commercial Fabric via Textile-Compatible Nanoscale Film Coating Process for Fibertronics Hagyoul Bae†, Byung Chul Jang†\$, Hongkeun Park‡, Soo-Ho Jung¹, Hye Moon Lee¹ , Jun-Young Park†, Seung-Bae Jeen†, Oyeongho Son†, Il-Woong Teho†, Kyoungsik Yu†, Sung Gap Im², Sung-Yool Cho솧, and Yang-Kyu Cho솆 , Soo-Ho Jung², Hye Moon Lee¹ , Jun-Young Park†, Seung-Bae Jeen†, Oyeongho Son†, Il-Woong Teho†, Kyoungsik Yu†, Sung Gap Im², Sung-Yool Cho솧, and Yang-Kyu Cho솆, Soo-Hoo Jung², Jung², Soo-Hoo Jung², Jung², Soo-Hoo Jung², Jung

volatile power-hungry electronic components, and modest battery storage. Here, we report a novel poly(ethylene glycol dimethacrylate) (PEGDMA)-textile memristive nonvolatile logic-in-memory circuit, enabling normally off computing, that can overcome those challenges. To form the metal electrode and resistive switching layer, strands of cotton yarn were coated with aluminum (AI) using a solution dip coating method, and the pEGDMA was conformally applied using an initiated chemical vapor deposition process. The intersection of two Al/pEGDMA coated yarns becomes a unit memristor in the lattice structure. The pEGDMA-Textile Memristor (ETM), a form of crossbar array, was interwoven using a grid of Al/pEGDMA coated yarns and untreated yarns. The former were employed in the active memristor and the latter suppressed cell-to-cell disturbance. We experimentally demonstrated for the first time that the basic Boolean functions, including a half adder as well as NOT, NOR, OR, AND, and NAND logic gates, are successfully implemented with the ETM crossbar array on a fabric substrate. This research may represent a breakthrough development for practical wearable and smart fibertronics.

The research team also demonstrated that the basic Boolean Anothers, including NOT, NOB, OB, AND, and NASD, logic gates, were reliably includemented for date encogating and storage within the ETH WEST decision area. Total entering large functional Block. It was just commissed for the storage of the storage block. It was just commissed for energy-efficient wearable (been storage). The storage of the storage o

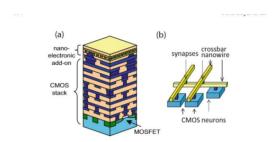

Fig. 6.1 CMOL circuits. (a) A cartoon of a hybrid CMOS/memristor integrated circuit. (b) The example of three CMOS cells (neurons) interconnected via corresponding crossbar nanowires (dendrites and axons) and cross-point memristive devices (synapses), which are located above CMOS layer

Table 1.2 Summary of the desirable performance metrics for synaptic devices

| Performance metrics       | Desired targets                       |

|---------------------------|---------------------------------------|

| Device dimension          | <10 nm                                |

| Multilevel states' number | >100°                                 |

| Energy consumption        | <10 fJ/programming pulse              |

| Dynamic range             | >100°                                 |

| Retention                 | >10 years <sup>a</sup>                |

| Endurance                 | >10 <sup>9</sup> updates <sup>a</sup> |

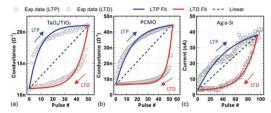

Linearity in Weight Update The linearity in weight update refers to the linearity of the curve between the device conductance and the number of identical programming pulses. Ideally, this should be a linear relationship for the direct mapping of the weights in the algorithms to the conductance in the devices. However, the resistive synaptic devices generally have the nonlinearity in weight update (see Fig. 1.3). The trajectory of the long-term-potentiation (LTP) process that increases the conductance differs from that of the long-term-depression (LTD) process that decreases the conductance. The weight tends to saturate at the end of LTP or LTD processes. This nonlinearity is undesired because the change of the weight ( $\Delta$ W) depends on the current weight (W), or in other words, the weight update has a history dependence. Recent results have shown that this nonlinearity has caused the learning accuracy loss in the neural networks [41, 42].

Programming Energy Consumption The estimated energy consumption per synaptic event is around 1 ~ 10 fl in biological synapses. Most RRAM/CBRAM devices show a programming energy around 100 fl ~ 10 pJ, while most PCM devices may have even higher programming energy 10 ~ 100 pJ. The fundamental challenge is that it is much more difficult (thus paying more energy) to move the ions/defects in solid-state devices than moving calcium ions in the liquid environment in biological synapses. A back-of-envelope calculation is given as follows. In biological synapses, the spike voltage is −10 mV, the ionic current ~1 nA, and the spike period ~1 ms; therefore, the energy is about 10 fJ. In resistive synaptic devices, the typical programming voltage is −1 V, and the programming current is typically ~µA; atthough the programming speed can be accelerated less than the real time to be <µs, still the energy is on the order of pJ. Further device engineering is thus needed to reduce the energy consumption.

requirement of NVM. The number of endurance is much application dependent, relying on how many weight updates are required in the training processes. For a relatively simple task (i.e., the MNIST handwritten digit recognition [43]), 60,000 training images with 50 training epochs (to repeated) give a maximum weight update possibility to be  $3\times10^6$  updates. Actually not every synapse is updated in the training; thus, an endurance  $\sim10^4$  is sufficient for training MNIST dataset [19]. However, considering more challenging tasks (i.e., ImageNet challenge [44]), much more endurance may be required.

Uniformity and Variability Poor uniformity or significant variability in emerging NVMs is a major barrier for digital memory applications. In contrast, the neural networks promise robustness against device variations. The device variations could partially be tolerated by two mechanisms: the massive (thus maybe redundant) connections between neuron nodes by synaptic arrays and the iterative weight update process during the training. The degree of variations that can be tolerated at the system level strongly depends on the network architecture and the accuracy required by the target application. The device-algorithm co-simulations have shown the reasonable robustness against device variations in different neural networks [42, 45].

Retention and Endurance During the online training, the weights are frequently updated, and the data retention requirement can be relaxed. When the training is complete, the resistive synaptic should behave as a long-term memory with a data retention in the order of 10 years at elevated temperature similarly as the

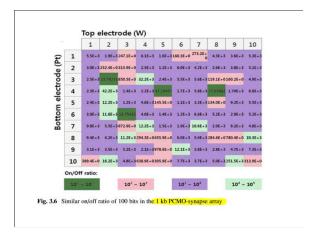

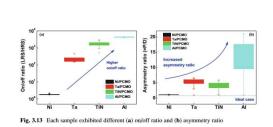

Fig. 1.3 The measured nonlinearity in the weight update reported from the literature: (a)  $TaO_x/TiO_2$  device [39], (b) PCMO device [36], and (c) Ag:a-Si device [33]

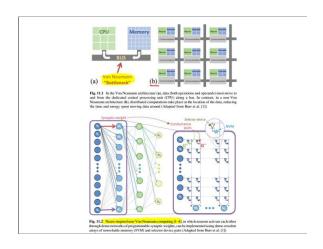

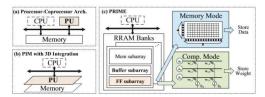

Fig. 10.1 (a) Traditional processor-coprocessor architecture with shared memory; (b) PIM architecture using 3D integration technologies; (c) PRIME design

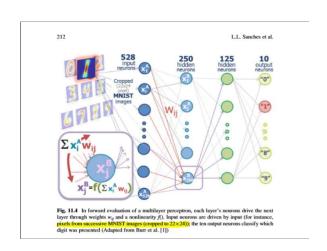

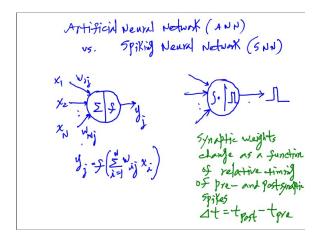

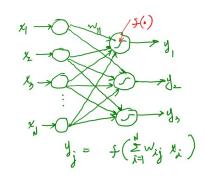

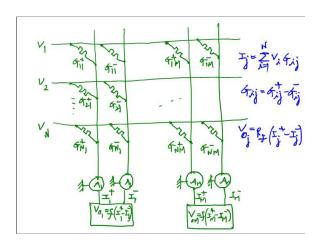

## Forward Propagation $x^{B}_{j} = f(\sum w_{ij} x^{A}_{i})$ f(.): non-linear activation $y^{B}_{j} = f(\sum w_{ij} x^{A}_{i})$ f(.): non-linear activation $y^{B}_{j} = f(\sum w_{ij} x^{A}_{i})$ f(.): non-linear activation $y^{B}_{j} = f(\sum w_{ij} x^{A}_{i})$ f(.): non-linear activation

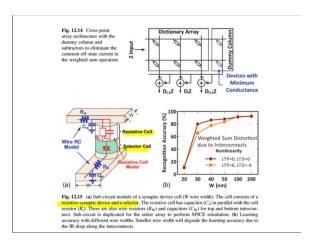

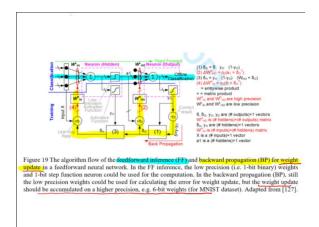

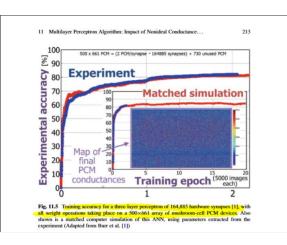

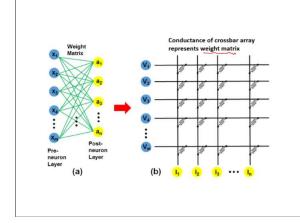

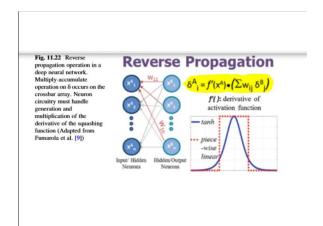

Fig. 11.21 Forward propagation operation in a deep neural network. The multiply-accumulate operation occurs on the crossbar array. Neuron circuitry must handle the nonlinear squashing function (Adapted from Fumarola et al. [9])

Accumulated Sum

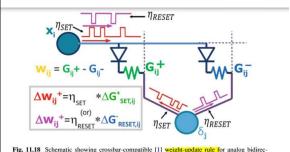

Fig. 11.18 Schematic showing crossbar-compatible [1] weight-update rule for analog bidirectional NVMs. Weight increases (decreases) can be implemented either as a SET operation on  $G^+$  ( $G^-$ ) or a RESET operation on  $G^-$  ( $G^+$ ) devices. Asymmetry in the partial SET and RESET operation is compensated by applying a different learning rate parameter ( $\eta_{\rm SET}$ ,  $\eta_{\rm RESET}$ ) that modulates the number of pulses fired from the neurons into the array (Adapted from Fumarola et al. [9])