# 5 ub threshold operation

### Opportunities for Ultra-Low Voltage

- Number of applications emerging that do not need high performance, only extremely low power dissipation

- Examples:

- Standby operation for mobile components

- Implanted electronics and artificial senses

Smart objects, fabrics, and e-textiles

- Need power levels below 1 mW (even μW in certain cases)

Slide 11.4

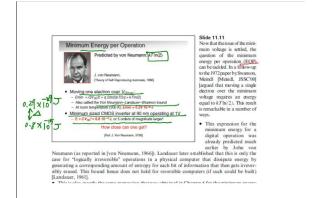

Although keeping the power density constant is one motivation for the continued search to lower the EOP, another, maybe even more important, reason is the exciting applications that only become feasible at very low energy/power levels. Consider, for instance, the digital wrist-watch. The concept, though straightforward, only became attractive once the power dissipation

[R1]

of clarity. For low values of  $V_{DS}$ , the DIBL effect can be ignored

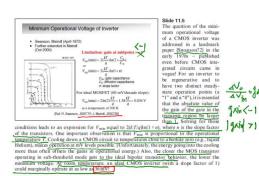

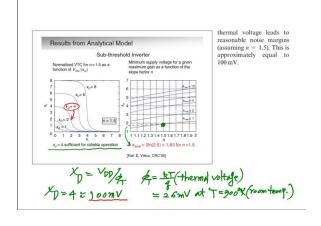

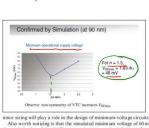

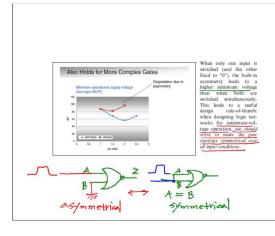

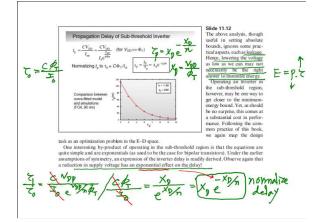

sistor sizing will play a role in the design of minimum-voltage circuits. This implies it falls worth noticing is that the simulated minimum voltage of 60 mV is slightly higher theoretical value of 45 mV. This is mostly owing to the definition of "operational" point. A the invester is only marginally functional. In the simulation, we assume a small m approximately 25 mV.

# Grand Challenges in the Near-term (Through 2020) and Long-term (2021 and Beyond)

## LOGIC DEVICE SCALING [PROCESS INTEGRATION, DEVICES, AND STRUCTURES, EMERGING RESEARCH DEVICES, FRONT END PROCESSES, MODELING AND SIMULATION, AND METROLOGY]

The conventional path of scaling planar CMOS will face significant challenges set by performance and powe consumption requirements.

Reduction of the equivalent gate exide thickness (EOT) will continue to be a difficult challenge in the near term despite the introduction of high-s metal gate (HKMG), Integration of highe-s materials while limiting the fundamental increase in gate tunneling currents due to band-gap narrowing are also challenges to be faced. The complete gate stack material systems need to be optimized together for best device characteristics (power and performance) and cost.

New device architecture such as multiple-gate MOSFETs (e.g., finFETs) and ultra-thin body FD-SOI are expected. A particularly challenging issue is the control of the thickness, including its variability, of these ultra-thin MOSFETs. The solutions for these issues should be pursued concurrently with circuit design and system architecture improvement.

High mobility channel materials such as Ge and III-V have been considered as an enhancement or replacement for Si channel for CMOS logic applications. High-s metal gate dielectric with low interface trap density (DIT), low bulk traps and leakage, unpinned Fermi level and low obmic contact resistances are major challenges.

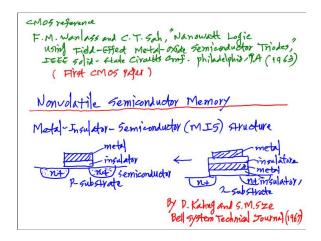

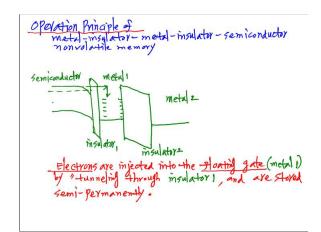

## MEMORY DEVICE SCALING [PROCESS INTEGRATION, DEVICES, AND STRUCTURES, EMERGING RESEARCH DEVICES, FRONT-END PROCESSES, MODELING AND SIMULATION, AND METROLOGY]

The challenges for DRAM devices are adequate <u>storage capacitance</u> with reduced feature size, high-x delectrics implementation, low leakage access device design, and low sheet resistance materials for bit and word lines. The drive to 4Pe<sup>2</sup> type cell to increase bit density and to lower production cost will require high aspect ratio and non-planar FET structures.

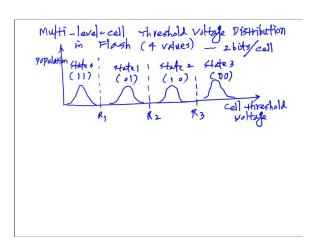

Flash memory has become a new FEOL technology driver for critical dimension scaling, materials and processing (lithography, etching, etc.) technology, abcad of DRAM and logic. Continued Flash density improvements in the near term rely on the linkchienes scaling of the tunned oxide and the intergate delectric. To guarantee the charge retention and endurance requirements, the introduction of high-x materials will be necessary. Cost effective implementation of 3-D AND flash bysood 256 flow with MLC and acceptable reliability performance remains and difficult inhallenge. New challenges also include the inception aito main/remrementative of new memory types and storage concepts such angueric RAM (MRAM), phase-change memory (TSM). Ressiver RAM EndAM and termelectric RAM TelRASA).

| Year of Production                                              | 2013      | 2015      | 2017        | 2019     | 2021     | 2023     | 2025     | 2028     |

|-----------------------------------------------------------------|-----------|-----------|-------------|----------|----------|----------|----------|----------|

| Logic Industry "Node Name" Label                                | *16/14*   | *10*      | *7*         | *5*      | '3.5"    | *2.5*    | "1.8"    |          |

| Logic to Pitch (nm)                                             | 40        | 32        | 25          | 20       | 16       | 13       | 10       | 7        |

| Flash % Pitch [2D] (nm)                                         | 18        | 15        | 13          | 11       | 9        | 8        | 8        | 8        |

| DRAM 1/2 Pitch (nos)                                            | 28        | 24        | 20          | 17       | 14       | 12       | 10       | 7.7      |

| FinFET Fin Half-pitch (new) (nm)                                | 30        | 24        | 19          | 15       | 12       | 9.5      | 7.5      | 5.3      |

| FinFET Fin Width (new) (nm)                                     | 7.6       | 7.2       | 6.8         | 6.4      | 6.1      | 5.7      | 5.4      | 5.0      |

| 6-r SRAM Cell Sigr(um2) [#60]2]                                 | 0.096     | 0.061     | 0.038       | 0.024    | 0.015    | 0.010    | 0.0060   | 0.0030   |

| MPU/ASIC HighPerf 4s NAND Gase Styr(um2)                        | 0.248     | 0.157     | 0.099       | 0.062    | 0.039    | 0.025    | 0.018    | 0.009    |

| 4-input NAND Gate Density (Kgateshum) [#155f2]                  | 4.03E+03  | 6.37E+03  | 1.01E+04    | 1.61E+04 | 2.55E+04 | 4.05E+04 | 6.42E+04 | 1.28E+05 |

| Flush Generations Label (hits per chip) (SLOMLC)                | 64G /128G | 128G/256G | 256G / 512G | 512G/1T  | 512G/1T  | 1T/2T    | 2T / 4T  | 4T / 8T  |

| Flash 3D Number of Layer targets (at relaxed Poly half pitch)   | 16-32     | 16-32     | 16-32       | 32-64    | 48-96    | 64-128   | 96-192   | 192-384  |

| Flash 3D Layer half-pitch turgets (nm)                          | 64nm      | 54nm      | 45nm        | 30nm     | 28nm     | 27nm     | 25nm     | 22nm     |

| DRAM Generations Label (bits per chip)                          | 40        | 8G        | 86          | 16G      | 320      | 32G      | 32G      | 320      |

| 450mm Production High Volume Manufacturing Begins (100Kuspm)    |           |           |             | 2018     |          |          |          |          |

| Vild (High Performance, high Vild transistors)f**f              | 0.86      | 0.83      | 0.80        | 0.77     | 0.74     | 0.71     | 0.68     | 0.64     |

| LACVII ) (Lipsec) [**]                                          | 1.13      | 1.53      | 1.75        | 1.97     | 2.10     | 2.29     | 2.52     | 3.17     |

| On-chip local clock MPU HP [at 4% CAGR]                         | 5.50      | 5.95      | 6.44        | 6.96     | 7.53     | 8.14     | 8.8      | 9.9      |

| Maximum number wiring levels functionged                        | 13        | 13        | 14          | 14       | 15       | 15       | 16       | .17      |

| MPU High-Performance (HP) Printed Gate Length (GLpr) (nm) [**]  | 28        | 22        | 18          | 14       | 11       | 9        | 7        | (5)      |

| MPU High-Performance Physical Gate Length (GLph) (nm) [**]      | 20        | 17        | 14          | 12       | 10       | 8        | 7        | 5        |

| ASICLew Standby Power (LP) Physical Gate Length (nm) (GLph)[**] | 23        | 19        | 16          | 13       | 11       | 9        | 8        | 6        |

\*\* Note: from the PIDS working group data; however, the calibration of Vdd, GLph, and UCV is ongoing for improved targets in 2014 ITRS work

6