### Extending our calculations to a collection of nodes

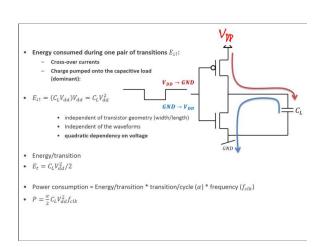

Average energy dissipated per computation cycle for one circuit node

$$E_{chk} = \frac{\alpha_k}{2} E_{ch\,cyc\,k} = \frac{\alpha_k}{2} C_k U_{dd}^2 \qquad \left( V_{dd} = V_{dd} \right)$$

Average energy dissipated per computation cycle in a voltage domain of K nodes

$$E_{ch} = \sum_{k=1}^{K} E_{ch\,k} = U_{dd}^2 \sum_{k=1}^{K} \frac{\alpha_k}{2} C_k$$

# Node activity (aka switching activity)

- Fact: Not all nodes within a (sub)circuit do change state at the same rate.

- Definition

A node's activity  $\underline{\alpha_k}$  indicates how many times per computation cycle node k switches from one logic state to the opposite one when averaged over many computation cycles.

- Examples:

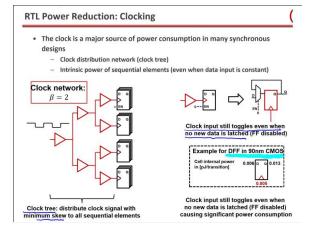

- Ungated clock in single-edge-triggered clocking:  $\alpha_k=2$

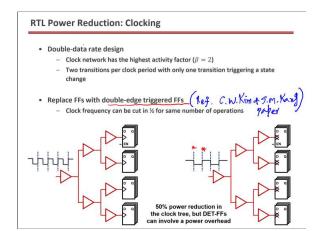

- Ungated clock in dual-edge-triggered clocking:  $lpha_k=1$

- Output of a T-type Flip-Flop if permanently enabled:  $lpha_k=1$

- Output of a D-type Flip-Flop fed with random data:  $lpha_k=1/2$

## Impact of Glitching

- In a synchronous (single-edge triggered) circuit, the activity factor of each node should never rise above  $\alpha_k=1/2$

- Reality: activity factors up to 6 or more can be observed:

- Increased activity due to glitches: signals reconverge after having propagated along paths of markedly different depths

- Glitching explains why the isomorphic architecture often dissipates more (dynamic) energy than more sophisticated architectures do.

- Activity caused by glitches is very difficult to predict (depends heavily on timing)

- Analytical prediction almost impossible

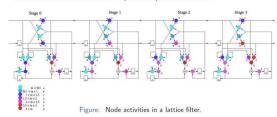

Node activities are distributed very unevenly in most circuits.

Activity increases with the number of preceeding logic stages (increased glitching)

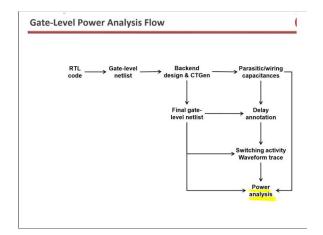

#### • Power consumption is divided into

- Net switching power

- Internal power

- Internal power depends on actual input values

- Power is consumed even if output does not change

- Library files: internal energy characterization for each cell at given supply voltage.

- Internal energy (cross-current, switching) per change in each input and output (as functions of input slope  $t_{r,\ell}$  and output load C)

- Contribution to capacitance of the connected net (input/output load)

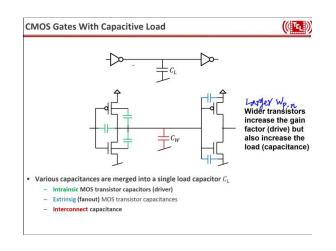

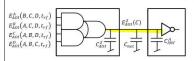

$$C = C_{AOI}^Z + C_{net} + C_{INV}^A$$

#### What about the activity factor(s)?

Fixed activity:

Assume a constant activity factor for all nodes in the circuit

Very rough estimate and highly inaccurate

• Statistical power analysis: e.g. CREST (by F. Najm et al.)

Assumes a given toggle activity at the input and propagates the activity throughout the circuit using statistical models of the gates

- Does not account for correlation between signal values

- No accounting for glitching activity

Simulation based:

Obtains toggle statistics from gate level simulations

- Most accurate method

- Slow

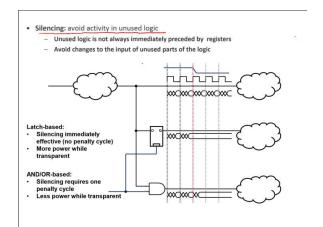

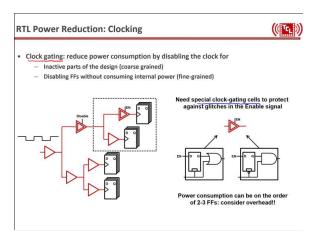

The clock is a major source of power consumption in many synchronous designs

Memory

Mem

J. Rabaey: Power figures from sever microprocessors and DSPs

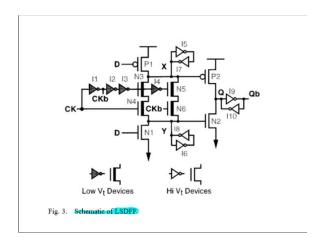

Brief Papers

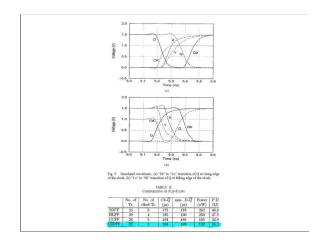

A Low-Swing Clock Double-Edge Triggered Flip-Flop

Chulwoo Kim, Momber, IEEE, and Sung-Mo (Steve) Kang, Fellow, IEEE

Abstract—A low-wing clock double-edge triggered flip flog

(LSDFF) is developed to order opener consumption significantly

compared to conventional flip-flops. The LSDFF worlds unare

evary internal ander transitions in red refere power consumption in clock distribution networks.

Several small awing clocking schemes have been proposed and

their potential for practical applications has been shown [3], [4].

The power swips in flip flog good preferance of egraptions as Tellow

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock, how 1/4 transitions or 100

LSDFF airs 1800 Wing clock wing flip-flop for halfwing clocking does not need high power-supply voltage but has a

long transition.