[Res. 1]

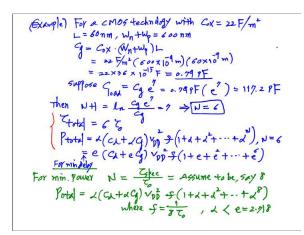

## Dynamic Power Consumption

Power = Energy per transition × Transition rate

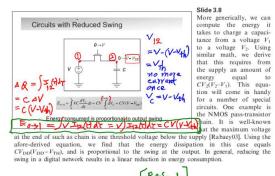

- $=C_{\rm L}V_{\rm DD}{}^2f_{0\rightarrow 1}$

- $= C_L V_{DD}^2 f P_{0 \to 1}$

- $= C_{\rm switched} V_{\rm DD}{}^2 f$

- $\begin{array}{ll} \bullet & \text{Power dissipation is data dependent} \text{depends} \\ \text{on the switching probability}, \rho_{0\rightarrow1} \\ \bullet & \text{Switched capacitance} C_{\text{switched}} = \rho_{0\rightarrow1} C_{\text{L}} = \alpha C_{\text{L}} \\ \text{($\alpha$ is called the switching activity factor)} \end{array}$

Slide 3.12

This brings us back to the generic case of the CMOS inverter. To translate the derived energy per operation into power, it must be multiplied with the rate of power-consuming transitions fo--i. The unit of the resulting metric is Watt (= Joules/sec). This translation leads right away to one of the hardest problems in power analysis and optimization: it requires knowledge of the "activity" of the circuit. Consider a circuit > 1 transition at a given clock.

with a clock frequency f. The probability that a node will make a 0-to-1 transition at a given clock tick is given by  $\pi f$ , where  $0 \le \pi \le 1$  is the activity factor at that node. As we discuss in the following sides,  $\pi$  is a function of the circuit topology and the activity of the input signals. The accuracy of power estimation depends largely upon how well the activity is known — which is most often not very much.

[RI]

Slide 3.13

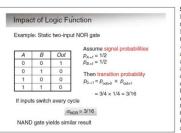

Let us, for instance, derive the activity of a two-input NOR gate (which defines the topology of the circuit). Assume that each input has an equal probability of being a 1 or a 0, and that the probability of a transition at a clock tick is 50-50 as well, ensuring an even distribution ensuring an even distribution between states. With the aid of the truth table we derive that the probability of a 0→1 transition (or the activity) equals 3/16. More generally, the activity at the output node can be expressed as a

function of the 1-probabilities of the inputs A and B:  $\alpha_{NOR} = p_A p_B (1 - p_A p_B)$ .

[R]

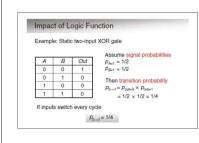

A similar analysis can be performed for an XOR gate. The observed activity is a bit higher (1/4).

[R,]

OR  $(1-p_A)(1-p_B)(1-(1-p_A)(1-p_B))$ XOR  $(1-(p_A+p_B-2p_Ap_B))(p_A+p_B-2p_Ap_B)$

Activity for static CMOS gates  $\alpha = p_0 p_1$

Slide 3.15 These results can be gener-alized for all basic gates.

Slide 3.16

Slide 3.16

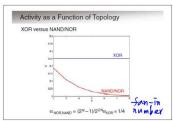

The topology of the logic network has a major impact on the activity. This is nicely illustrated by comparing the activity of NAND (NOR) and XOR gates as a function of fanin. The output-transition probability of a NAND gate goes asymptotically to zero. The probability of the output being a 0 is indeed becoming smaller with increasing fanin. An example of such a network is a memory-address decondenders decondenders decondended to the control of the control

der. On the other hand, the activity of an XOR network is independent of fan-in. This does not bode well for the power dissipation of modules such as large en(de)cryption and coding functions, which primarily consist of XORs.

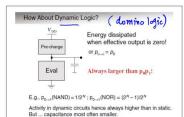

activity and capacitance, the latter being smaller in dynamic logic. In general though, the higher activity outweighs the capacitance

Slide 3.18

Slide 3.18

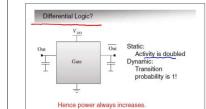

Another interesting logic family is differential logic, which may seem attractive for very low-voltage designs due to its increased signal-to-noise ratio. Differential implementations ferential implementations come unfortunately with an inherent disadvantage from a power perspective: not only is the overall capa-citance higher, the activity is higher as well (for both static and dynamic imple-mentations). The only

positive argument is that differential implementation reduces the number of gates needed for a given function, and thus reduces the length of the critical path.

static power analysis seem

Slide 3.21

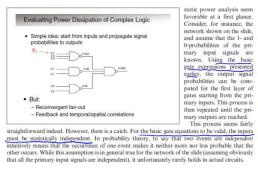

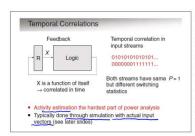

The story gets complicated even further by the occureven lurther by the occur-rence of temporal correla-tions. A signal shows tem-poral correlation if a data value in the signal stream is dependent upon previous values in the stream. Temporal correlations are the poral correlations are the norm in sequential net-works, as any signal in the network is typically a func-tion of its previous values owing to the existence of feedback network. In addi-

tion, primary input signals as well may show temporal dependence. For example, in a digitized speech signal any sample value

as well may snow temporal dependence. For example, in a digitized speech signal any sample vatue is dependent upon the previous values.

All these arguments help to illustrate that static activity analysis is a very hard problem indeed, and actually all but impossible. Hence, power analysis tools either rely on simulations of actual signal traces to derive the signal probabilities or make simplifying assumptions—for instance, it is assumed that the input signals are independent and purely random. This is discussed in more detail in Chapter 12. In the following chapters, we will most often assume that activity of a module in its typical operation mode can be characterized by an independent parameter α.

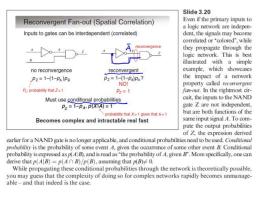

Slide 3.20

Even if the primary inputs to a logic network are indepen-dent, the signals may become correlated or "colored", while they propagate through the logic network. This is best illustrated with a simple example, which showcases